1 Pontificium Supraconductivum Limitator Currentus Defectus

1.1 Structura et Principium Operativum Pontificii SFCL

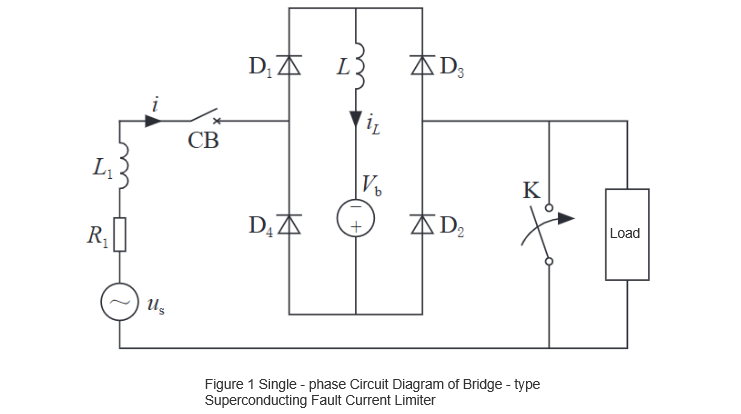

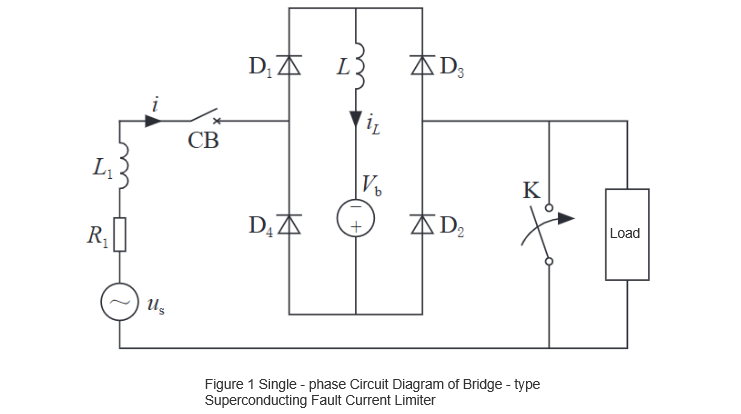

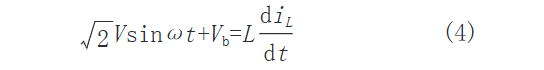

Figura 1 ostendit diagrammam circuiti uniphasici pontificii SFCL, quae constat ex quattuor diodis D₁ ad D₄, fonte voltus V_b pro praesetitione DC, et supraconductivo coil L. Interruptor circuitus CB est in serie cum limitatore ad interpellandum currentem defectus postquam fuit limitatum. Fontes V_b praebent currentem praesetitionis i_b ad supraconductivum coil L. Voltus V_b est ita altus ut superet cadentiam voltus directi diodorum (D₁ et D₃, vel D₂ et D₄), instituens currentem praesetitionis i₀. Valorem i₀ statuunt maior quam valorem maximam currentis lineae i_max, cum margine pro conditionibus overload.

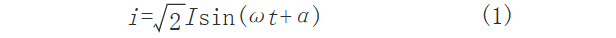

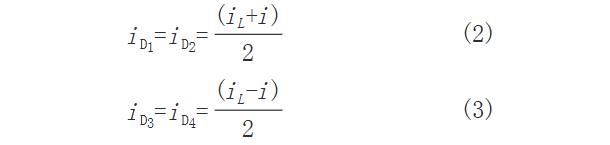

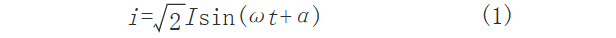

Itaque, sub normalibus conditionibus, ponticulus diodarum manet continuo conducens, et SFCL non exhibet impedimentum aliquod ad currentem lineae i, neglecta minori cadentia voltus trans pontem. Assumentes quod, sub normali operatione, currentes per diodas D₁ ad D₄ sunt iD1 ad iD4 respective, currentem lineae est:

Hoc obtinetur secundum Legem Kirchhoff de Currentibus (KCL):

Cum defectus short-circuit occurrat in linea, currentem lineae cito crescit ad i₀. In semicycli positivi et negativi, una pars diodarum fit reversa praesetita et clauditur, ideoque automatica inseritur coil L in circuitum. Ita currentem defectus limitatur per reactantiam inductivam coil.

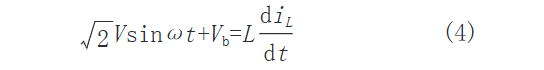

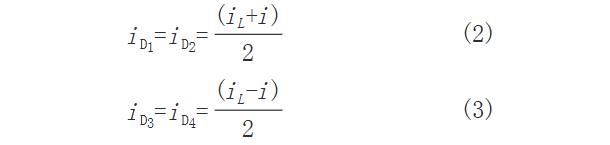

Ponendo currentem criticum supraconductivi coil convenienter, coil remanet in statu supraconductivo sub defectu, evitans effectus temporis responsionis et restitutio ab extinguendo. Tamen, ut defectus persistit, currentem per supraconductivum inductor continuat crescere, tandem accedens ad valorem steady-state currentis short-circuit qui esset sine limitatore. Itaque, fons defectus debet interpellari tempore definito per interruptor circuitus. Pro simplicitate, assumitur quod defectus short-circuit occurrat instantaneo quando voltus fontis transit per zero (t = t₀). Secundum Legem Kirchhoff de Voltibus (KVL), haec aequatio obtinetur:

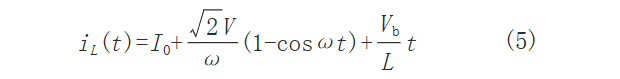

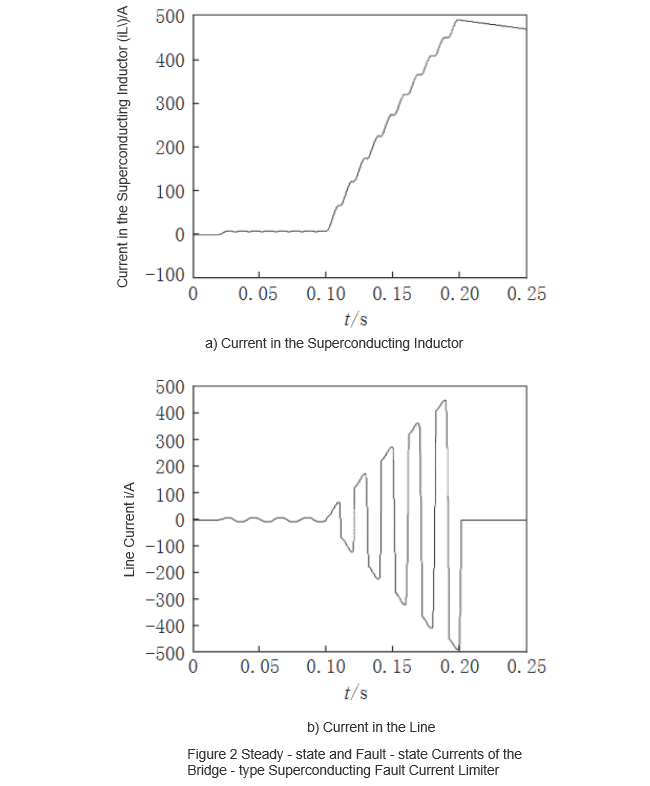

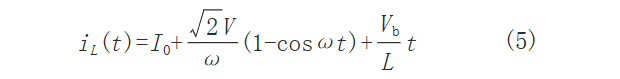

Condicio initialis iL(t0)=I0, solvendo hanc aequationem differentialem obtinetur:

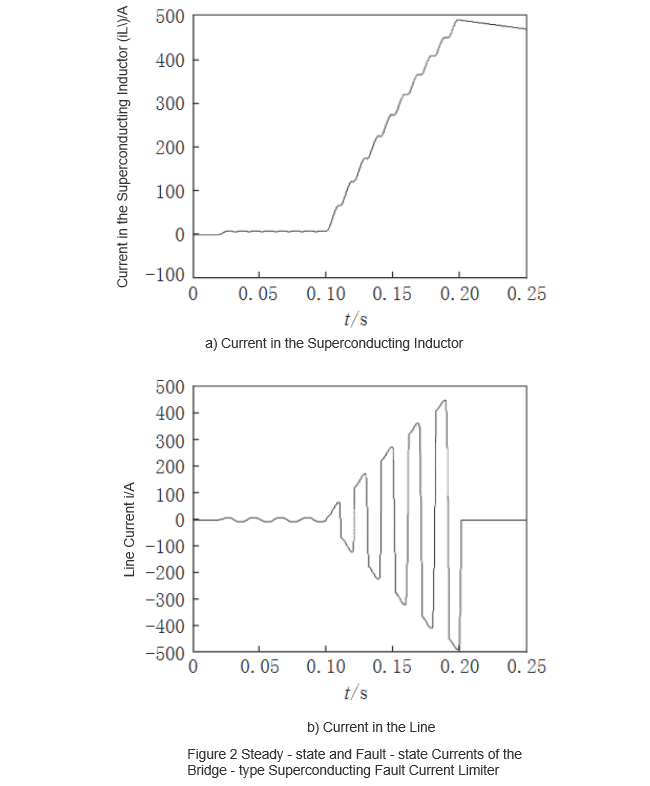

Figura 2 ostendit formas currentis inductoris et currentis lineae sub normali operatione et post defectum, cum defectus initium habeat t = 0.1 s. Resultata simulationis indicant quod currentem short-circuit cito crescit propter effectum limitantis supraconductivi inductoris. Processus limitantis est essentialiter magnetizatio supraconductivi inductoris. Cum currentem defectus stabilizatur, limitator cessat efficere. Itaque, defectus debet interpellari per interruptor circuitus antequam currentem short-circuit attingit suum valorem steady-state. In figura, defectus interpellatur per interruptor circuitus t = 0.2 s.

1.2 Melioramentum Structurae Pontificii Supraconductivi Limitatorum Currentus Defectus

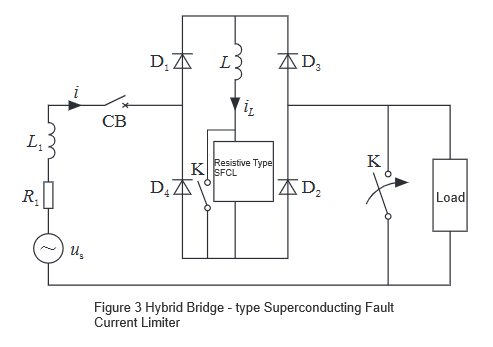

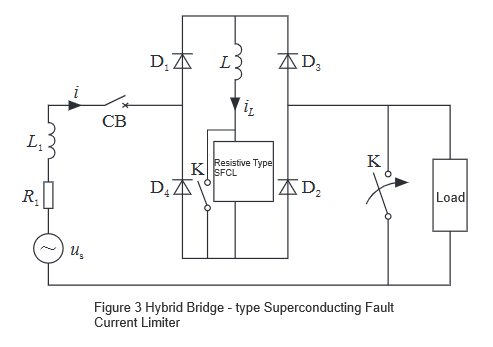

Pontificius supraconductivus limitator currentus defectus (SFCL) vulgaris tantum potest comprimere celeritatem crescendi currentis short-circuit, sed inefficax est in controllo eorum valorum steady-state. Ut limitentur valores steady-state currentis short-circuit, SFCL hybridus combinat characteres resistencie nullius in statu supraconductivo et celeris incrementi resistencie sub extinguendo supraconductorum. Hoc efficitur integrando limitatores supraconductivos resistive cum SFCL pontificiis. Diagramma schematicum huius approprati hybridici ostenditur in Figura 3.

Sub normalibus conditionibus operationis, commutator K est apertus, ideo SFCL resistivus non exhibet impedimentum externum, permitiens currentem i_L transire sine resistencia. Cum defectus occurrit, SFCL resistivus immediate praesentat alta impedimenta et operatur in serie cum supraconductivo inductor ad simul cohibendum currentem defectus. Post defectum interpellatum, commutator K clauditur; tunc, ob sua propria alta impedimenta, SFCL resistivus circumducitur et cito redit ad statum supraconductivum.

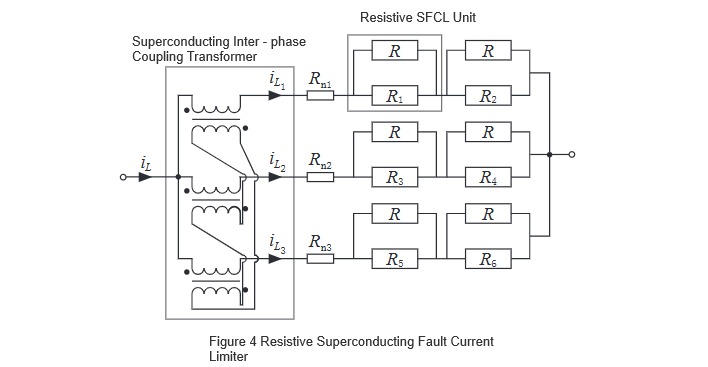

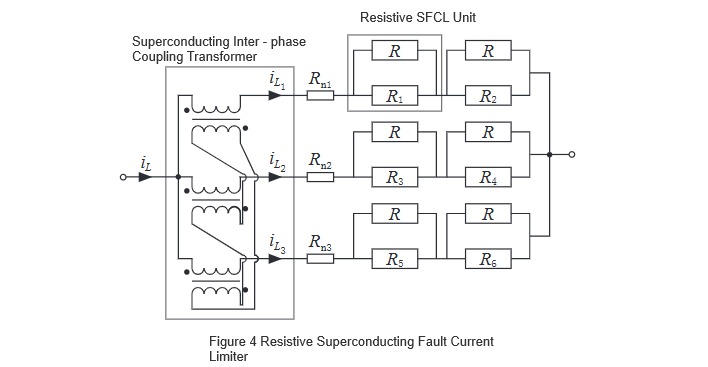

Quia commutator K habet resistenciam on-state, circumducetur per recuperatum SFCL resistivum, faciendo ut totus limitator pontificius hybridus appareat sicut impeditio parva externe. Tunc, aperiens K concludit totum processum limitantis. Ad augmentandam capacitem SFCL resistivum, saepe usurpantur connectiones series et parallelae unitatum SFCL resistivorum ad meliorandos gradus voltus et currentis apparati. Figura 4 ostendit schemata circuiti limitatoris supraconductivi resistivum, ubi R₁ ad R₆ representant resistentias supraconductivas, et R servit ut resistentia bypass quae potest provocare simultaneum extinguendum duorum supraconductorum in eadem rama series sub defectu short-circuit.

Officium transformatoris interphasialis est assecurare iL1 = iL2 = iL3, ut unitates SFCL diversarum ramarum parallelarum possint simultane extinguere post defectum short-circuit. SFCL pontificius hybridus efficaciter limitat valores steady-state currentis short-circuit utilizando transitionem supraconductori ab statu supraconductivo ad normalem (S/N), automatica ingrediens resistentiam limitantis post detectionem defectus absque necessitate mechanismorum additionis detectionis defectus. Tamen, additio dispositivi limitantis supraconductivi resistivum augmentat costus operationales generales et prolongat tempus restitutionis ab extinguendo, complicando coordinationem cum operationibus reclosure systematis.

2 Pontificius Non-Supraconductivus Limitator Currentus Defectus

2.1 Limitator Currentus Solid-State

In recentibus annis, rapidi progressus in technologia electronicorum potentiae et dispositivis semiconductorum potentiae magnae capacitatis — sicut SCR, GTO, GTR, et IGBT — cum suis amplis applicationibus in systematibus practicis, fecerunt limitatores currentus defectus compositos ex inductoribus, resistentiis, condensatoribus, et componentibus electronicorum potentiae esse focus studii. Limitator pontificius non-supraconductivus constructus est ex componentibus vulgari, vitans technologiam complexam supraconductivam, et offert beneficia alta fiducialitas et boni costus-effectivitas.

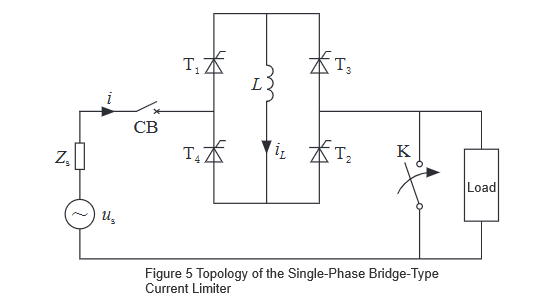

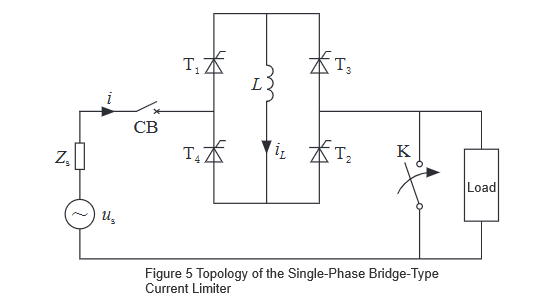

Figura 5 ostendit diagramma schematicum idealis limitatoris currentus pontificii uniphasici, constans ex circuitu pontis uniphasico et inductore limitante L. Sub normali operatione, impulsus continui applicantur ad quattuor thyristores. Post breve processum magnetizationis, currentem in inductore attingit valorem maximam currentis oneris. Quando cadentia voltus trans thyristores T₁ ad T₄ negliguntur, limitator non exhibet impedimentum externum.

Si defectus short-circuit occurrit in semicyclo positivo voltus fontis, T₃ cogitur claudere, inserendo inductorem limitantem in circuitum ad comprimendum currentem defectus. Poniendo convenienter valorem inductoris L, currentem short-circuit potest limitari ad quodlibet desideratum. Praeterea, hic limitator habet facultatem instantaneae interpellationis currentis short-circuit. Tamen, ob usum quattuor commutatorum controllabilium, logica controlis pro interpellatione instantanea est relative complexa. Sub limitando currentem defectus, harmonics significantes generantur; haec possumus efficaciter mitigari connectendo inductores bypass in parallelum trans brachia pontis.

2.2 Pontificius Semicontrolatus Limitator Currentus Defectus Short-Circuit

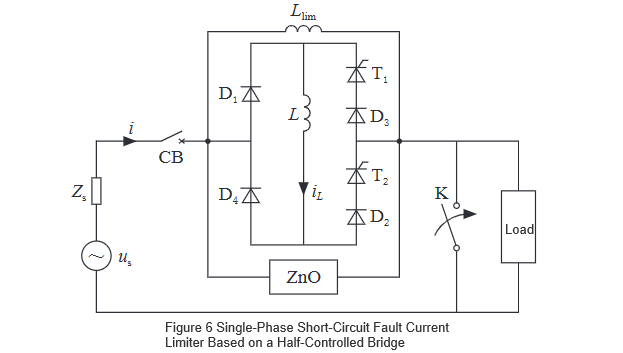

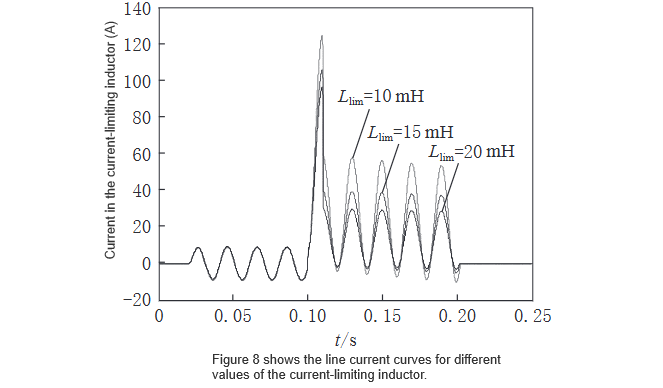

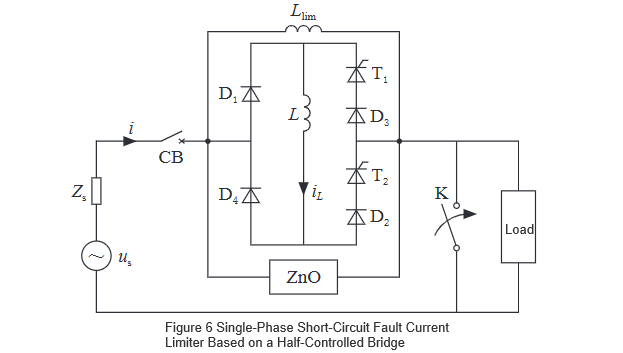

Figura 6 illustrat topologiam limitatoris currentus defectus short-circuit uniphasici basata in ponte semicontrolato et dispositivis self-turn-off. Hoc systema constat ex diodis D₁ ad D₄, dispositivis self-turn-off T₁ et T₂, supraconductivo inductore L, inductore limitante Llim, et absorbente overvoltage ZnO, cum us representante fontem AC et CB serviente ut interruptor circuitus lineae.

Sub normalibus conditionibus operationis, duo dispositiva self-turn-off T₁ et T₂ sunt continuo activata. Post initial power-up, currentem in supraconductivo inductore gradualiter crescit ad valorem maximam currentis lineae sub influentia fontis voltus. Postquam onus stabilizatur, iL remanet constans. Neglectis cadentiis voltus directi trans diodas D₁ ad D₄ et dispositiva self-turn-off T₁ et T₂, voltus trans pontem est zero, et voltus trans inductorem limitantem Llim quoque est zero. Itaque, limitator currentus non exhibet impedimentum externum nec impactum in systema.

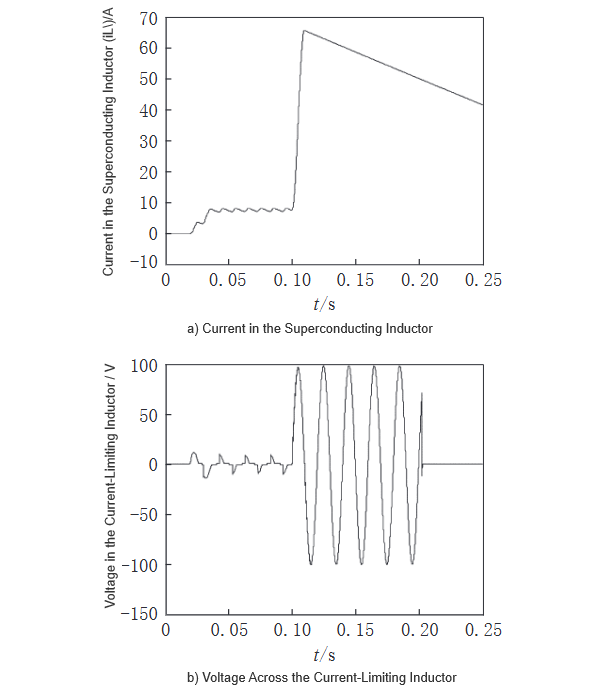

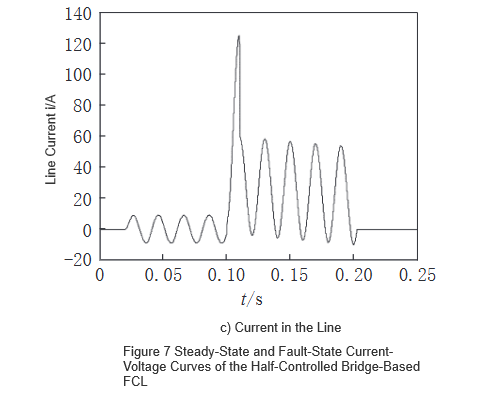

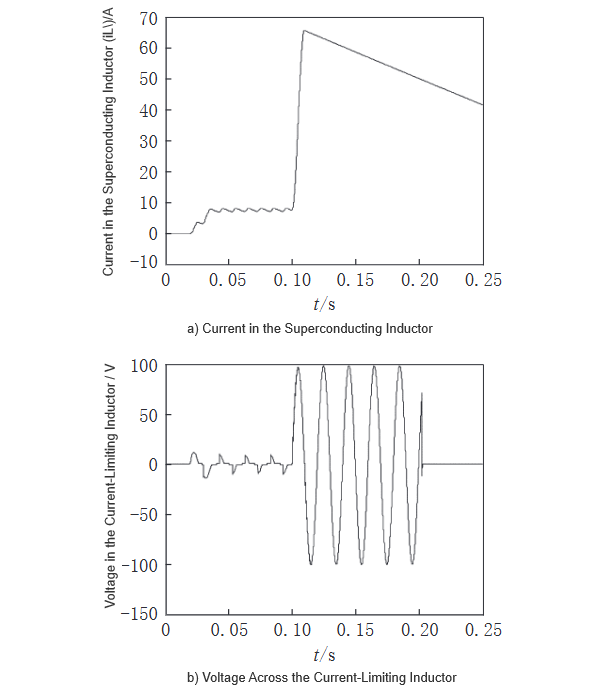

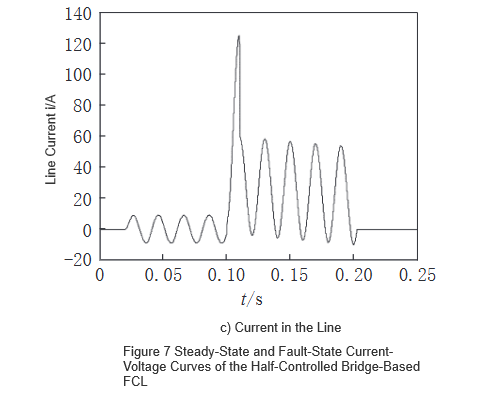

Cum defectus short-circuit occurrit in systema, currentem iL in supraconductivo inductore crescit. Post detectionem defectus short-circuit, T₁ et T₂ statim clauduntur, faciendo ut ponticulus exit operationem. Currentem short-circuit tunc transferitur ad inductorem bypass Llim, dum currentem in supraconductivo inductore continuat fluere trans diodas D₁ et D₄ donec decrescat ad zero. Figura 7 ostendit curvas currentis et voltus status steady-state et defectus limitatoris currentus defectus short-circuit uniphasici basati in ponte semicontrolato.

Systema potestur in t=0.02 secunda et attingit status steady-state intra unum cyclus. Defectus short-circuit occurrit in t=0.1 secunda, et T₁ clauditur intra quartum cyclus post detectionem defectus. Parametri circuiti usi pro simulatione sunt sequentes: valorem maximam phase voltus fontis est 100V/50Hz; valorem maximam rated oneris currentis est 10A; resistencia oneris est 10Ω; supraconductivus DC inductor L est 10mH; cadentia voltus directa trans diodas et commutatores controllabiles est 0.8V; et inductor limitans Llim est 10mH.

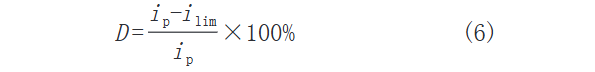

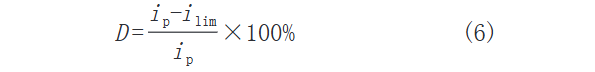

Unus principium usus limitatorum supraconductivorum currentus defectus (SFCL) in systematibus potentiae est limitare currentes defectus ut non excedant capacitates interruptoris instantanei circuitus lineae. In analysis, ratio reductiva currentis defectus DD (0<D<10<D<1) communiter usatur ad representandum percentage reductivum valorem maximam currentis defectus, et expressio pro DD est:

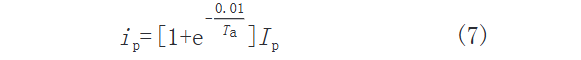

ip est peak inrush current durante short-circuit sine SFCL installato, et eius valorem est relatus ad rationem equivalentis X/RX/R systematis.

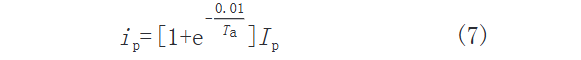

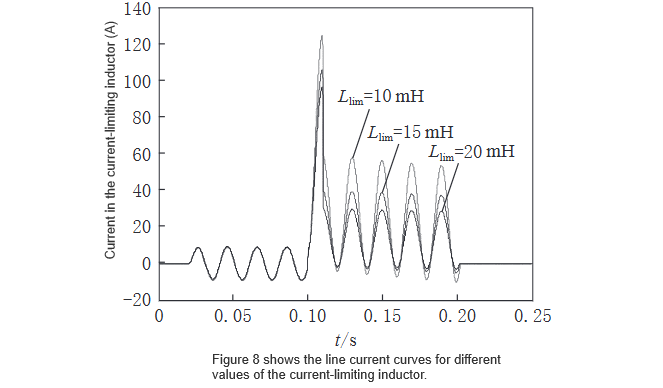

In Aequatione (7), IpIp denotat amplitudinem periodicam componentis currentis short-circuit, et TaTa est constantia temporis. ilimilim repraesentat valorem maximam currentis short-circuit limitati, qui dependet a magnitudine inductoris limitantis LlimLlim. Poniendo convenienter valorem LlimLlim, desideratum percentage reductivum valorem maximam currentis defectus potest attingi. Simulationes fuerunt conductae cum LlimLlim set to 10 mH, 15 mH, and 20 mH, et resultata ostenduntur in Figura 8. Potest observari quod maior LlimLlim praebet melius performance limitantis, sed etiam ducit ad maiora costus operationales.

2.3 Melioramentum Pontificii Semicontrolati Limitatoris Currentus Defectus Short-Circuit

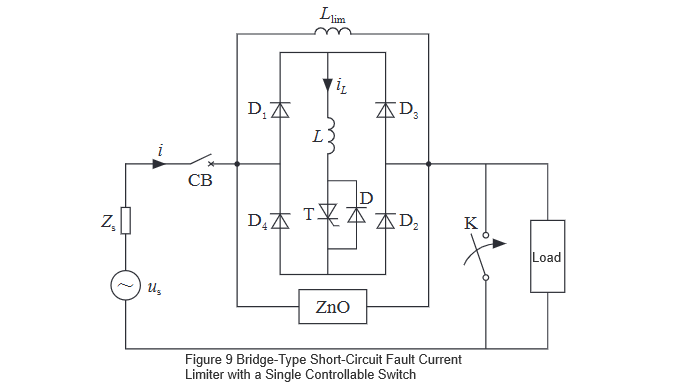

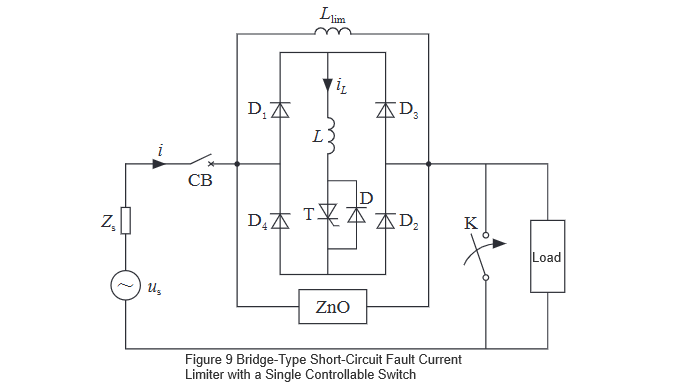

In configuratione ostenta in Figura 6, T₁ et T₂ sunt continuo activata sub normalibus conditionibus operationis. Postquam defectus short-circuit detectus est, circuitus controlis claudit utrumque T₁ et T₂. Ponendo unum commutatorium controllabile T in via communali pontis pro T₁ et T₂, simile effectum limitantis potest attingi. Haec modificatio reducit numerum componentum controllabilium, minuit costus, et simplificat complexitatem circuiti. Schemata diagrammatica ostenditur in Figura 9.

3 Conclusio

Hoc opus praesentat varios genera pontificiorum limitatorum currentus defectus short-circuit. Cascadando limitatorem supraconductivum pontificium vulgarem cum limitatore supraconductivo resistivum, tam valorem maximam quam valorem steady-state currentis short-circuit potest efficaciter limitari. Praeterea, utendo characteribus S/N (supraconductivus ad normalem) materialium supraconductivorum, systema integra detectionem defectus, activationem, et limitationem currentis in unum unitatem, praebens rapidam responsionem et altam fiducialitatem.

In recentibus annis, cum rapido progressu et practica applicatione technologiae electronicorum potentiae et dispositivorum electronicorum potentiae magnae capacitatis, limitatores currentus defectus short-circuit pontificii non-supraconductivi — compositi ex commutatoribus electronicorum potentiae vulgaribus et inductoribus — acceperunt beneficia alta fiducialitas et costus-effectivitas propter absentiam technologiae complexae supraconductivae. Resultata simulationum demonstrant utrumque genus limitatorum currentis attingere excellentem performance limitantis, confirmantes feasibility approaches limitantis currentis propositarum.