1 Technicae Difficultates

1.1 Stabilitas Parallela Dispositorum

In applicationibus practicis, capacitas portandi currentem unius dispositivi electronici potestatis est relativiter limitata. Ad exigentias alti currentis satisfaciendas, saepe plura dispositiva in parallelum iunguntur. Tamen variationes parametrorum inter dispositiva—sicut leves differentiae in resistencia onus et voltantia liminis—possunt causare distributionem inaequalitatem currentis in operatione parallela. In transitiis commutationis, inductantia parasitica et capacitancia adhuc ducunt ad mutationes inaequales celeritatum currentis inter dispositiva parallela, exacerbantes inaequationem currentis. Si non cito solvitur, haec inaequatio certa dispositiva supercalere et deficere potest propter excessivum currentem, ita ut vita utendi circuito interruptore solid-state minuatur.

1.2 Morae Detectionis Defectus

In systematibus DC, characteristica currentis defectus valde differunt ab systematibus AC, carentes punctis zero-crossing quae adiuvant in detectione et interruptione defectus. Hoc postulat ut circuiti interruptores solid-state utantur algorithmis detectionis defectus microsecond-level ad accurate identificandum defectus et rapidam responsionem. Methodi traditionales detectionis defectus laborant sub moris notabilibus cum currentibus defectus DC rapidis variabilibus, facientes eas non posse satisfacere exigentiis protectionis velox.

1.3 Contradictio Inter Dispersionem Caloris et Volumen

Ad satisfaciendum modernis systematibus potestatis de alta densitate potestatis, designa circuiti interruptoris solid-state debent maiorem potestatem tractare intra spatium limitatum. Tamen alta densitas potestatis ducit ad acutam incrementum caloris generati per dispositiva electronica potestatis. Insufficientia dispersionis caloris causat temperaturas excessivas, degradantes performance dispositivi et possibiliter trigge randum fuga thermica et deficere apparatus. Technicae refrigerationis traditionales male perficiunt cum circuitis interruptoribus solid-state alta densitate potestatis. Licet refrigeratio liquida possit efficaciam dispersionis caloris meliorare, tamen incrementat magnitudinem et costum apparatus. Itaque, quomodo balanciare refrigerationem efficientem cum controllo rationabili voluminis—efficiendo optimisationem synergisticam—manet clavis difficultas in designo circuiti interruptoris solid-state.

2 Investigatio Technologiae Clavium

2.1 Technologia Applicationis Dispositorum Largi Bandgap

(1) Selectio et Packaging SiC MOSFET

Inter varia dispositiva largi bandgap, SiC MOSFETs parvi conduction-loss praebent significantes adventagia. Ad eorum performance in applicationibus multi-dispositivorum paralleli meliorandam, adoptatur layout DBC (Direct Bonded Copper) symmetria. Hic layout efficaciter reducit inductantiam parasiticam, quae crucialis est ad meliorandas characteristicae commutationis dispositivi. In commutatione, praesertim in turn-off, interactio inter inductantiam parasiticam et capacitancia dispositivi causat oscillationem voltantis gatii. Experimenta demonstrant quod cum layout DBC symmetria, oscillatio voltantis gatii in turn-off controllari potest ad minus quam 5%. Hoc non solum meliorat stabilitatem dynamicam in operatione parallela, sed etiam reducit periculum damni dispositivi causatum per oscillationem voltantis.

(2) Controllo Condivisionis Currentis Dynamicae

Ad difficultatem inaequationis currentis in dispositivis parallelis solvendam, introducitur strategia controllo combinans bus condivisionis currentis cum regulatione PI adaptativa. Bus condivisionis currentis, per structuram designi unicam, praebet viam distributionis currentis aequabilis pro singulis ramis parallelis in physico. Super hoc, algorithmus regulationis PI adaptativus dynamice adjustat signala drive singulorum dispositivorum basi monitoriationis real-time currentium ramicularum, efficiendo magis precisum controllo condivisionis currentis.

2.2 Technologia Celeris Detectionis et Interruptionis Defectus

(1) Detectio Defectus Basata in Voltanti Gatio

Analyse characteristicae defectus short-circuit SiC MOSFET revelat quod in defectu short-circuit, voltantia drain-source (VDS) rapidus ad 900V ascendit, dum voltantia gatii significanter descendit cum declinatione ultra 10 V/ns. Utens hac characteristica, comparatores dual-threshold designatur pro celeri detectio defectus, ponendo duos limites currentis: Ith1 = 500 A et Ith2 = 1.2 kA. Cum detectus currentis excedit Ith1, praeliminaris moneo triggeratur; excedendo Ith2 indicat defectum short-circuit confirmatum. Circuitus detectus et algoritmus processing signalis designati efficiunt moram detectionis tantum 0.8 μs. Hoc methodo circumvenit complexam conversionem et processing signalis methodorum traditionarum, utens inherentibus characteristicis electricis SiC MOSFET, significanter meliorando accuratam detectionis defectus.

(2) Strategia Interruptionis Optima Multa Obiectiva

Ad efficiendum high-performance interruptionem defectus in circuitis interruptoribus solid-state, tempus interruptionis (Δt), absorptio energiae (EMOV), et currentus inrush (Ipeak) poni ut obiectiva functiones, optimizatur utens algorithmo multi-objective particle swarm optimization (MOPSO). Tempus interruptionis brevius melius protegit equipmenta systematis; absorptio energiae afficit selectionem et longevitatem componentium protectivorum sicut MOVs; excessivus currentus inrush causa stress electricus significantem, impediens normalis operationem equipmentorum.

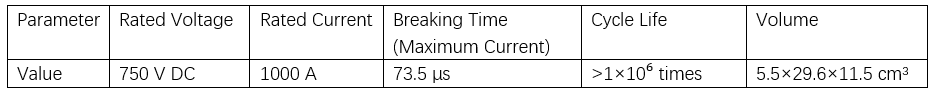

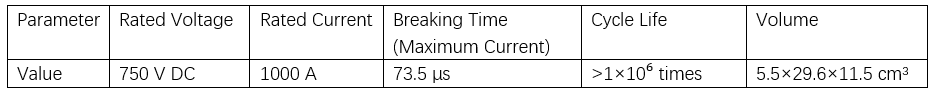

Per iterationes multas MOPSO optimationis, parameter optima determinantur: inductor current-limiting LB = 15 μH et coefficient voltage-limiting MOV γ = 1.8. Usis his parameteribus optimitate, tempus interruptionis reducitur ad 73.5 μs, et maximus currentus limitatur ad 526 A. Visu demonstrandum effectum optimisationis, methodus decisionis TOPSIS comparat resultatas ante et post optimisationem. Comparatio ostendit meliorationes significativas in indicatoribus clavis sicut tempus interruptionis, absorptio energiae, et currentus inrush, magne augmentando performance totale et melius satisfaciendo exigentiis practicalibus engineering pro interruptione celeri et fidebili a circuitis interruptoribus solid-state.

2.3 Design Structurae Mechanicae Altae Fidei

(1) Interruptor Isolator Permanens Magnetis

Ad meliorem fidem et stabilitatem circuitorum interruptorum solid-state, designatur interruptor isolator permanens magnetis utens mechanismo bistabile permanens magnetis. In hac structura, vis tenendi pro claudendo et aperiendo primarie praebetur a magnetibus permanentibus, cum spira energizatur tantum momentanea in operationibus commutationis. Hoc reducit consumptionem potestatis circa 90% comparata cum interruptoribus isolatoribus electromagneticis traditionibus. Analysa Adams dynamic simulation ostendit quod vita mechanica huius interruptoris isolatoris permanens magnetis excedit 1 million operationes, cum velocitate separationis contactuum 3 m/s. Alta velocitas separationis contactuum securitatem rapidam disconnectionis circuiti in occurrentia defectus, reducens probabilitatem generationis arcus et augmentando capability interruptionis switch. Longa vita mechanica securitatem stabilis performance in usu prolongato, reducens frequentiam maintenance et replacement, sic praebens fortem supportum pro efficienti operatione circuiti interruptoris solid-state.

(2) Solutio Managementis Caloris

Ad solvendum difficultates dispersionis caloris in designis altae densitatis potestatis, proponitur solutio cooling hybrida combinans evaporative cooling cum forced air cooling. Evaporative cooling utitur principium evaporationis liquidae absorbentis calorem, efficiens transferentiam caloris intra spatia compacta. Forced air cooling adhuc augmentat dispersionem caloris per convectionem forced fan-driven. Hoc methodo cooling hybrida stabilizat temperature hotspots moduli infra 75°C, cum rate incrementi temperature minor quam 5°C/min, satisfaciendo standardibus requirementibus.III. Verificatio Experimentalis

3 Verificatio Experimentalis

3.1 Parametri Prototypi

Ad verificandum effectivitatem technologiae clavium et schemata designi, prototypus circuiti interruptoris DC low-voltage solid-state developatur, cum principibus parametri sequentibus:

3.2 Resultata Test Type

Test type comprehensives conducti sunt in prototypum ad evaluandum num performance eius satisfacit exigentiis applicationum practicalium:

(1) Test Interruptionis Short-Circuit

Defectus short-circuit inter severissimos defectus in systematibus potestatis, et instantaneus currentus enormis qui generatur posit periculum significantem operationi equipmentorum. Ad simulandum hanc conditionem extremam, test environment 23 kA short-circuit current establishitur—ponens rigorosum challenge pro circuito interruptore solid-state. In initio test, prototypus rapidus activatur, et eius integrata technologia celeris detectionis et interruptionis defectus incipit functionare. Haec technologia, per monitoring currentis high-precision et mechanismum rapidi response, detectat currentem abnormalis in tempore extremo brevi et immediate triggerat processum interruptionis.

In interruptione, personnel test observant proxime performance circuiti interruptoris, et nulla re-ignition arcus occurrit per totum processum. Hoc resultatum non solum demonstrat alta efficacia technologiae celeris detectionis et interruptionis defectus, sed etiam illustat superior performance interruptionis circuiti interruptoris solid-state. In circuitis interruptoribus traditionibus, re-ignition arcus est difficultas difficile evitanda, quae saepe ducit ad defectus secundarios vel etiam gravis damage equipmentorum. Contrario, circuitus interruptor solid-state successus evitat hanc problemam per advanced interruption techniques, sic praebens fortis supportum pro stabili operatione systematibus potestatis.

(2) Test Incrementi Temperaturae

Performance thermalis est alter factor clavis in evaluatione circuitorum interruptorum solid-state. Ad effective assessmentem capability dispersionis caloris devicei in operatione prolongata, test incrementi temperaturae conductus est. Prototypus requiritur operari continue per 24 horas, in qua calor significans generatur [9]. Post test, sensors temperature usi sunt ad mensurandum temperature prototypi. Resultata ostendunt incrementum temperature ΔT = 32 K. Hoc data confirmat effectivitatem solutionis cooling hybridae combinantis evaporative cooling et forced air cooling. Integrando principium naturalis dispersionis caloris evaporative cooling cum convectione forced air cooling, systema efficaciter dissipat calorem generatum in operatione, securans device intra acceptabilem rangem temperature. Bonum management caloris non solum securat stabile operationem circuiti interruptoris solid-state, sed etiam extendit longevitatem eius.

(3) Test Vitae

Vita service est index criticus in determinatione num circuitus interruptor solid-state possit latae applicari in realibus systematibus potestatis. Itaque, ad verificandum suum performance vitae, prototypus subiit test endurance unius millionis operational cycles. Per totum test, personnel proxime monitoraverunt mutationes in resistance contactuum prototypi. Post test, resistance contactuum mensurata et inventa mutata minus quam 5%. Hoc resultatum validat effectivitatem designi longae vitae interruptoris isolatoris permanens magnetis. Etiam post operationes prolongatas et frequentes, contactus switch maintinet excellentem conductivity, securans fidelem functionem on/off circuiti interruptoris solid-state.

4 Conclusio

In summa, huius scriptum praebet solutionem technicam circuiti interruptoris DC low-voltage solid-state basata in investigatione profunda technologiae clavium, includens optimisationem dispositivorum largi bandgap, algoritmos intelligentis controllo, et design structurae altae fidei. Verificatio experimentalis ostendit quod prototypus developatus efficit leading performance in indicatoribus clavis sicut celeritas interruptionis, accuratudo detectionis defectus, et longevitas operationis.

Successus efficit interruptionem microsecond-level celerem et vitam operationis unius millionis cycle, praebens solutionem practicam et feasible pro protectione in systematibus distributionis potestatis novae energiae. Prospiciente, sunt multae promissae directiones research pro circuitis interruptoribus DC low-voltage solid-state. Exempli gratia, establishment modeli simulationis integrationis dispositivo-packaging-system level potest plus comprehensive simulare performance circuitorum interruptorum solid-state sub variis conditionibus operationis, sic praebens supportum theoreticum plus accurate pro optimisatione designi.